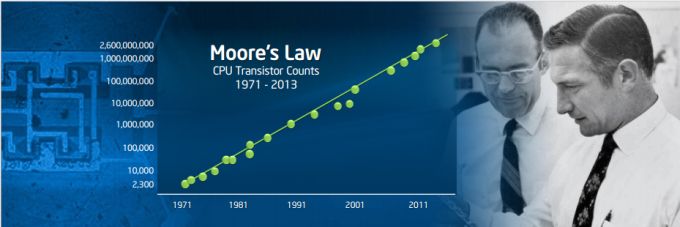

Fue en abril de 1965, hace por tanto medio siglo, que Gordon Moore, por entonces en Fairchild y luego cofundador de Intel, publicó un artículo en la revista Electronics que postulaba que cada dos años, aproximadamente, se podría fabricar un chip que tuviera el mismo tamaño pero el doble de elementos básicos (transistores), tesis que ha dado en llamarse ley de Moore. La reducción del coste a la mitad cada dos años, su principal consecuencia, ha sido el motor del desarrollo de la industria de semiconductores y, por extensión de toda la tecnología digital desde entonces. En 1974, Robert Dennard, empleado de IBM, formuló matemáticamente el principio del escalado de los semiconductores.

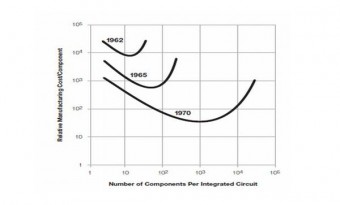

A nadie se le ha ocurrido hablar de una «ley de Dennard», pero aquella observación de Moore suele presentarse como algo inmutable e irreversible, lo que en parte ha sido un mérito del marketing de Intel. Hay una buena razón industrial para que así ocurra: si se reduce el tamaño de un transistor, se consigue más rapidez y menos consumo proporcional de energía. El único objetivo de la industria de semiconductores ha sido, por tanto, reducir el tamaño de los chips para aumentar su rendimiento y su velocidad. Además, al ser más pequeños, resultaban más baratos, con las consecuencias de todos conocidas.

Sin embargo, la observación de Moore se está agotando, y dentro de pocos años no se podrá reducir mucho más el tamaño de los chips de manera rentable. No obstante, aun queda mucho recorrido para fabricar semiconductores más complejos y multifuncionales, gracias a lo cual la industria electrónica podrá innovar más aún en el diseño y seguir inundando el mercado con dispositivos más económicos, variados y diminutos.

Recapitulando: la fabricación de semiconductores a gran escala se inició a finales de los 60 del pasado siglo. Durante tres décadas, hasta 1998, se pudo duplicar cada dos años sin mayores problemas el número de componentes por chip. La tecnología CMOS sobre sustrato de silicio se reveló extremadamente versátil y capaz de seguir el ritmo frenético que describía la ´ley de Moore`. Esos treinta años conforman la era clásica del escalado (o reducción) progresiva de los chips.

A finales de los 90, sin embargo, se vio que la energía aplicada a los transistores no se podía seguir reduciendo proporcionalmente a su tamaño, y que la llamada corriente de fuga aumentaba sin cesar. En consecuencia, los chips se calentaban mucho y las prestaciones caían en picado: había puntos más calientes que en el núcleo de una central nuclear. Ese fue el final de la carrera de los gigahercios en los microprocesadores, que había sido la bandera comercial de la época.

En los últimos quince años, se han desarrollado tecnologías en parte paliativas del consumo exponencial de energía, y han permitido seguir reduciendo el tamaño de los chips casi en la proporción histórica señalada por Moore: técnicas como el empleo de transistores de múltiples puertas, el uso de dieléctricos y aislantes especiales, y la colocación de compuestos de germanio sobre el sustrato de silicio. Pero los transistores no van sustancialmente más rápido y la tensión de suministro no ha bajado, pese a la reducción de tamaño de los chips.

La ventaja principal de la fabricación de semiconductores, a partir de 1999, y la consecuencia de que los transistores sean más pequeños ya no es, por tanto, el aumento de prestaciones, sino que se pueden poner más funciones en un chip. O, lo que es lo mismo, el coste por función es cada vez más bajo y previsiblemente seguirá así hasta finales de esta década o mediados de la siguiente (2020 a 2025). Un único chip podría hacer más cosas, muchas más, con un tamaño inferior a una uña y con un consumo de energía moderado.

Los chips están llegando a su límite de escalado: la reducción a la mitad de su tamaño cada dos años – aproximadamente – no se podrá mantener. La actual generación de semiconductores, fabricados con reglas de diseño de 14 nanómetros, quizá dará paso a la siguiente, de 10 nanómetros, en tres o cuatro años más, pero se duda que sea posible ir más allá, tanto por los límites físicos de la litografía como por el aumento de coste de producción para reducir el tamaño de los transistores.

La industria está entrando, así, en una nueva fase, caracterizada por la fabricación de chips con diseños mucho más complejos, que podrán hacer más funciones con un tamaño ínfimo y bajo consumo de energía, pero no necesariamente serán más baratos ni más potentes ni tendrán pistas por debajo de los 10 nanómetros. Esto ya supone una auténtica revolución en el diseño de los chips y por ende de las aplicaciones.

Hasta ahora, había muy pocos incentivos en innovar en el diseño de los chips, porque el ritmo de miniaturización era tan frenético que no daba tiempo a incluir los nuevos diseños en los sistemas de fabricación más punteros. Los chips a medida y con diseños más depurados, debían ser fabricados con sistemas de tres o cuatro generaciones anteriores. No es raro que un chip a medida esté fabricado con reglas de 45 nanómetros, mientras que las memorias o los procesadores ya son de 14 nanómetros.

Cuando, dentro de pocos años, se frene en seco la miniaturización, se tendrá tiempo para rediseñar y optimizar la configuración interna de los chips, lo que probablemente dará paso a una estructura de negocio diferente pero tanto o más disruptiva que la vigente hasta ahora. De hecho, la utilización masiva de chips – básicamente a medida – en los automóviles, está impulsando este cambio de la estructura de la industria electrónica.

Visto con perspectiva, el progreso de los semiconductores en estos 50 años desde el artículo de Moore en Electronics ha sido impresionante. El gráfico original de Moore no podía humanamente anticipar la magnitud de esta evolución. Naturalmente no se le puede culpar por ello, pero el intento de convertir la genialidad de su postulado en dogma ha creado injustamente confusión. Que muchas cosas han cambiado desde 1965, no hay quien lo niegue.

En la década de los 80, las reglas de diseño o tamaño de las pistas que separaban los transistores eran de unas pocas micras o milésimas de milímetro. En los 90 eran de unas décimas de micra, y a principios de este siglo se trabajaba ya a 0,13 micras, lo que dio pie a que se abandonaran las micras y se empezara a hablar de nanómetros (0,13 micras es igual a 130 nanómetros)

Segunda recapitulación: hasta ahora, la regla formulada por Moore se ha venido cumpliendo más o menos a rajatabla durante 50 años, porque la industria invertía lo necesario para que se cumpliera: se fabricaban chips de 90 nm en 2004, de 65 nm en 2006, de 45 nm en 2008, de 32 nm en 2010, de 22 nm en 2012 y de 16 nm a partir de 2014. Las compañías punteras (Intel, pero también Samsung y TSMC) fabrican chips a gran escala con reglas de diseño de 14 nm: los chips siguen siendo cada vez más pequeños y el coste por transistor es más bajo con cada generación, aunque ya no son ni mucho más potentes ni tampoco mucho más eficientes.

En estos momentos, se está trabajando en el desarrollo de la generación de 10 nanómetros, y experimentando con la de 7, para fabricar hacia el 2025 con reglas de 5 nanómetros. Aunque cada vez hay más dudas de que se pueda alcanzar, por los enormes retos que supone. Intel aseguró, en la reciente conferencia de circuitos de estado sólido (ISSCC 2015) que a finales de 2016 o principios de 2017, fabricará chips de 10 nanómetros y el camino hacia los 7 ya lo tiene trazado. Pero subsiste un problema mayor que el tecnológico: no se piensa que sea rentable producir chips tan pequeños.

Una tercera etapa de la industria debería iniciarse, por tanto, en unos pocos años, a finales de esta década como máximo. El uso de strained silicon (silicio tensionado) y de grafeno, compuestos de germanio y de los grupos I, III y IV de la tabla periódica, debería hacerlo viable. Por su lado, la miniaturización continuará, con sistemas totalmente integrados, lo que se conoce como SoC (System-on-Chip) y se integrará no sólo contenido digital sino también analógico, de radiofrecuencias, componentes pasivos y de potencia, etcétera, que han dado en llamarse sistemas empaquetados o SiP (System-in-Package).

La combinación de SoC y SiP debería llevar al desarrollo de sistemas de muy alto valor añadido con más prestaciones, y un tamaño minúsculo y consumo energético mínimo. En un documento estratégico de 2013, significativamente titulado More than Moore, se explica que los chips tendrán en los próximos lustros mucha vida, a un ritmo igual o más trepidante que en el último medio siglo. Sería fascinante saber qué piensa el hombre que intuyó este camino, Gordon Moore, hoy de 86 años, retirado en Hawaii.

[informe de Lluís Alonso]